One of the challenges in the field of reliability of electronic components in the aerospace sector is the ability to characterize the malfunction rate (SEE) due to neutrons present at sea level, at high altitude and in spatial conditions, and identify mitigation procedures with special regard to commercial components (Commercial Off The Shelf-COTS). For over thirty years a UTOV team – from Eletronic Engeering and Physics Departments – has designed and developed neutron instrumentation at eV and MeV energies. During 2016-2018 the UTOV group characterized numerous electronic components (flash memories etc.) both by irradiation with fast neutrons and in the absence of irradiation, at the VESUVIO and ChipIr instruments at ISIS and collaborative research activities with national and international companies (Thales Alenia Space, ST Microelectronics, ESA, SOREQ) operating in aerospace.

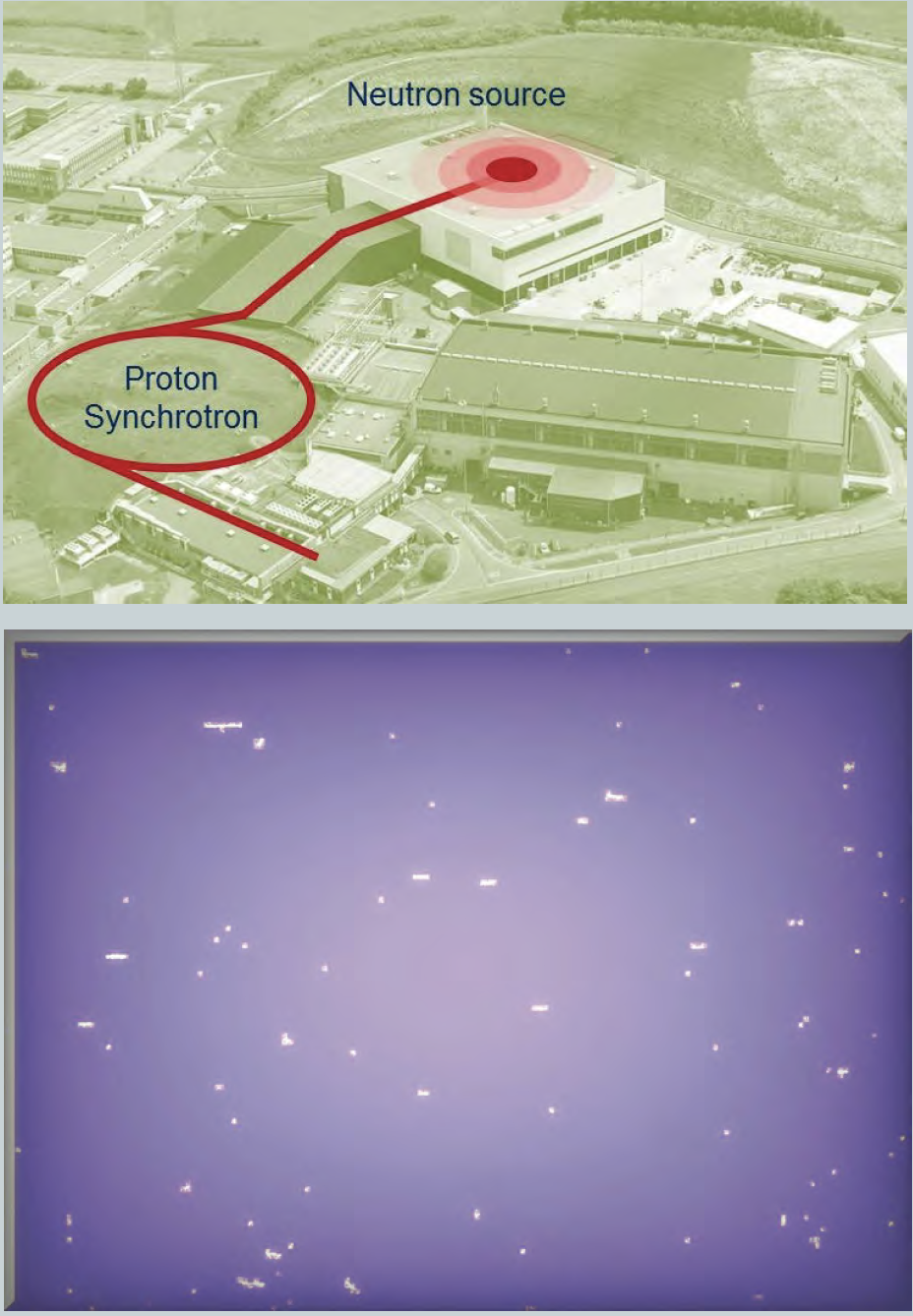

The top figure shows a schematics of the neutron production layout at ISIS. The bottom figure is a rendering of the charge generation clusters induced by the impact of the ChipIR neutron beam on a CCD for irradiation exposures of approximately 33 ms. The CCD was exposed at 90 degrees with respect to the CCD plane, therefore neutrons arrive sideways. Multiple (long) tracks clusters are due to fast energy neutrons. Single (dot-like) track clusters are due to low-energy neutrons.

With the creation of the Node, thanks to the new acquisitions of laboratory and instrumentation infrastructures, the team plans to start a program of new design and characterization of electronic devices (SRAM and FPGA memory cards) and COTS, to be realized – through the platform for “apply for beamtime” (see Section 2.2) – both at ISIS@MACH, and at ISIS, using the complementary neutron techniques of the ChIpir and VESUVIO beam lines.

References

[1] E . Fermi, Report for month ending December 15, 1942, Physics Division, USAEC Report CP-387, University of Chicago, 1942.

[2] D. Schaffer, L. Johnson, “Oak Ridge National Laboratory: The First Fifty Years” (The University of Tennessee Press, Knoxville) 1994.

[3] C. Andreani, A. Pietropaolo, A. Salsano, G. Gorini, M. Tardocchi, A. Paccagnella, S. C. D. Frost, S. Ansell, S. P. Platt, “Facility for fast neutron irradiation tests of electronics at the ISIS spallation neutron source”, Appl. Phys. Lett., 92 (2008) 114101.

[2] D. Schaffer, L. Johnson, “Oak Ridge National Laboratory: The First Fifty Years” (The University of Tennessee Press, Knoxville) 1994.

[3] C. Andreani, A. Pietropaolo, A. Salsano, G. Gorini, M. Tardocchi, A. Paccagnella, S. C. D. Frost, S. Ansell, S. P. Platt, “Facility for fast neutron irradiation tests of electronics at the ISIS spallation neutron source”, Appl. Phys. Lett., 92 (2008) 114101.

[4] C. Cazzaniga, S. P. Platt, C. D. Frost, “Preliminary Results of ChipIR, a new Atmospheric-like Neutron Beamline for the Irradiation of Microelectronics”, in Proceeding of the SELSE-13, 13th Workshop on Silicon Errors in Logic-System Effects”, 21-22 March 2017, Northeastern University, Boston, Massachusetts (USA).

[5] D. Onorati, C. Andreani, L. Arcidiacono, F. Fernandez-Alonso, G. Festa, M. Krzystyniak, G. Romanelli, P. Ulpiani, R. Senesi; “Gamma background characterization on VESUVIO: before and after the moderator upgrade”Journal of Physics: Conference Series, 1055 (1), 012009 (2018).

[5] D. Onorati, C. Andreani, L. Arcidiacono, F. Fernandez-Alonso, G. Festa, M. Krzystyniak, G. Romanelli, P. Ulpiani, R. Senesi; “Gamma background characterization on VESUVIO: before and after the moderator upgrade”Journal of Physics: Conference Series, 1055 (1), 012009 (2018).

[6] C. Andreani, R. Senesi, A. Paccagnella, M. Bagatin, S. Gerardin, C. Cazzaniga, C. D. Frost, P. Picozza, G. Gorini, R. Mancini, M. Sarno; “Fast neutron irradiation tests of Flash memories used in space environment at the ISIS spallation neutron source”AIP Advances 8, 025013 (2018).

[7] Fedi, M. Ottavi, G. Furano, A. Bruno, R. Senesi, C. Andreani, C. Cazzaniga, “High-energy neutrons characterization of a safety critical computing system,”IEEE International Symposium on Defect and Fault Tolerance in VLSI, and Nanotechnology Systems (DFT), Cambridge, United Kingdom, (2017), pp. 1-4. doi:10.1109/DFT.2017.8244456

[8] Gerardin, M. Bagatin, A. Ferrario, A. Paccagnella, A. Visconti, S. Beltrami, C. Andreani, G. Gorini, C. D. Frost, “Neutron-induced Upsets in NAND Floating Gate Memories”, Transactions on Device and Materials Reliability 12, 437-444, (2012), 10.1109/TDMR.2012.2192440

[9] M. Bagatin, S. Gerardin, A. Paccagnella, C. Andreani, G. Gorini, C. D. Frost, “Temperature Dependence of Neutron-induced Soft Errors in SRAMs”, Microelectronics Reliability 52 (1) 289-293 (2012), doi:10.1016/j.microrel.2011.08.011 Key.